You signed in with another tab or window. Reload to refresh your session.You signed out in another tab or window. Reload to refresh your session.You switched accounts on another tab or window. Reload to refresh your session.Dismiss alert

I spent at least a dozen hours learning Gowin FPGA PSRAM using your controller as an example. Nice job, thanks.

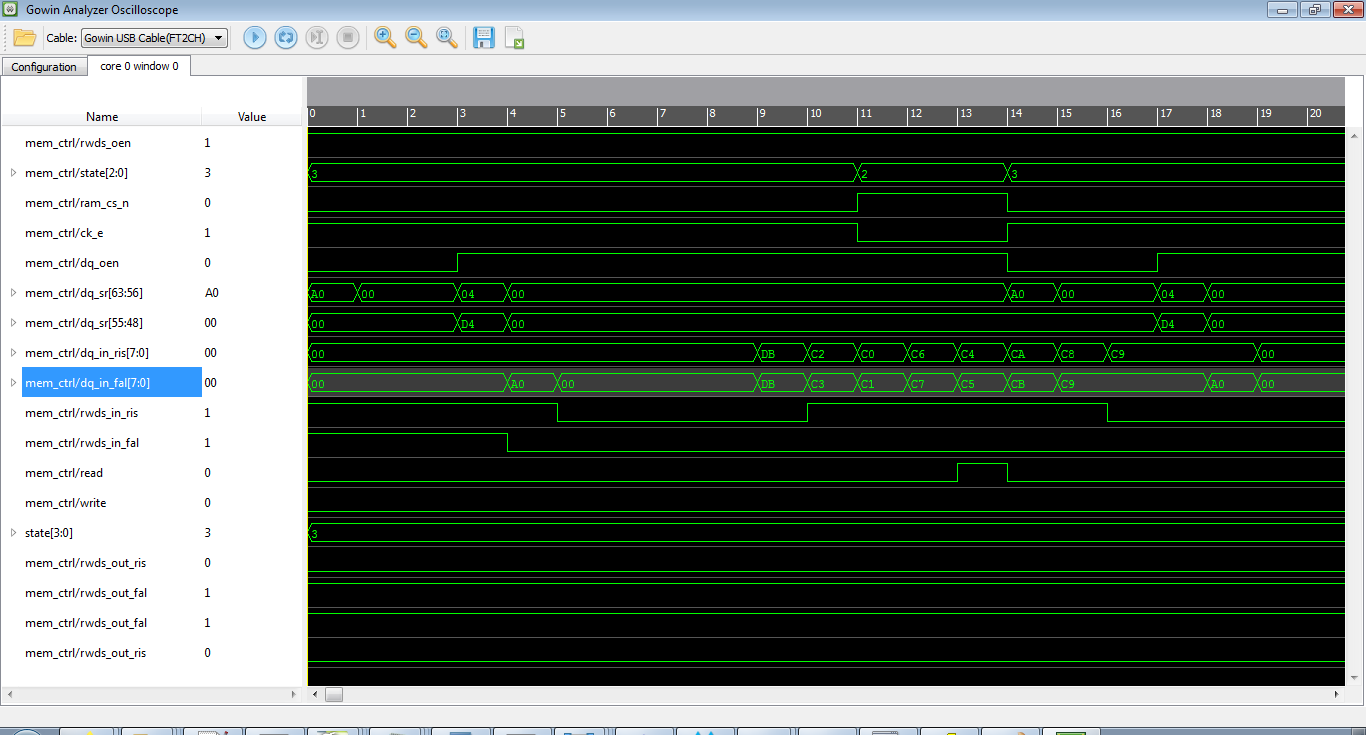

However I came across ambiguities while playing with Gowin Analyzer.

Can you explain why the memory keeps putting memory sample values on the bus after ck_e goes low. I'm talking about values on dq_in_ris and dq_in_fal after 10th clock cycle. 0xC3 and 0xC2 are proper values for adresses 0x0 and 0x1. But then goes 0xC1, 0xC0, 0xC7, 0xC6 which are correct values for next memory cells but shouldn't be here because ck_e is low.

I'm also having problems while trying to run the controller on clock frequencies of 30 MHz and below. Something is wrong with read waveforms and it reports "FAIL. Read wrong data."

The text was updated successfully, but these errors were encountered:

I spent at least a dozen hours learning Gowin FPGA PSRAM using your controller as an example. Nice job, thanks.

However I came across ambiguities while playing with Gowin Analyzer.

Can you explain why the memory keeps putting memory sample values on the bus after ck_e goes low. I'm talking about values on dq_in_ris and dq_in_fal after 10th clock cycle. 0xC3 and 0xC2 are proper values for adresses 0x0 and 0x1. But then goes 0xC1, 0xC0, 0xC7, 0xC6 which are correct values for next memory cells but shouldn't be here because ck_e is low.

I'm also having problems while trying to run the controller on clock frequencies of 30 MHz and below. Something is wrong with read waveforms and it reports "FAIL. Read wrong data."

The text was updated successfully, but these errors were encountered: